FPGA学习之高速ADC采集

ADC(Analog-to-Digital Converter,模拟-数字转换器)在硬件电路中是经常见到的器件,音频信号的采集、温度的采集等等,凡是涉及到模拟信号转数字信号的电路,都会用到ADC。

ADC的种类很多,有积分型的、逐次比较型的、SAR型的等等,各有各的优缺点及用途。一般根据实际的项目需求来选择ADC型号。

ADC有一个重要参数就是位宽,什么8位的、12位的、16位的,这其实就是ADC的分辨率,最小能分辨的输入电压大小。假设ADC的位宽为8位,参考电压为5V,最小分辨率为:1/2565V=0.0195V=19.5mV。如果实际项目需要对mV级别的模拟信号进行采集,那么8位的ADC满足不了需求,这个时候需要找更高位的ADC。

在实际的设计中,一个8位的ADC,其有效位并没有8位。由于芯片生产工艺的原因、电路设计的原因、电路板布局的原因等等,在这些因素的影响下,一个8位的ADC,其最后的2-3位是波动的,这个时候最后的2-3位是没有意义的,所以一个8位的ADC真正用到的只有高5-6位。

ADC还有一个常用的参数是采样率,采样率即一秒所能采的点的个数。在这里涉及到一个知识点:采样定律,根据内奎斯特采样定律可知,当采样频率大于等于两倍的输入信号的频率时,可从采集到的数据中恢复出原始信号。但是在实际的应用中,对一个正弦波进行采样时,采样频率至少是输入信号的10倍,这样可以采集到一个完整周期的正弦波信号。

ADC的指标还有好多,比如参考电压、带宽、精度等等,剩下的大家再细细研究哈,这里小编就不一一讲解了~~~~

下面我们来看看今天的主要内容

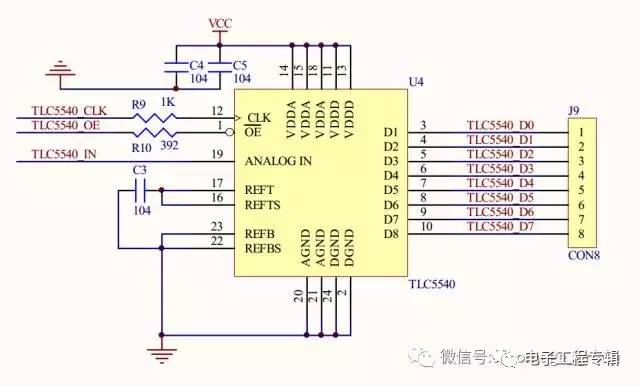

这是今天用到的ADC采集电路,从图中可以看出,ADC采集芯片为TLC5540,且其输出为8根数据线,或者也可以说是并行输出。

还是和之前一样,找TLC5540的数据手册,根据数据手册进行FPGA编程。

TLC5540是一个8位的高速ADC,其最大采样率为40MHz。

这是TLC5540芯片的时序,从图中可以看出,当OE(输出使能)=0时,在时钟的下降沿,可得到一个8位的数据,这个数据就是输入的模拟电压转化之后对应的数字量。

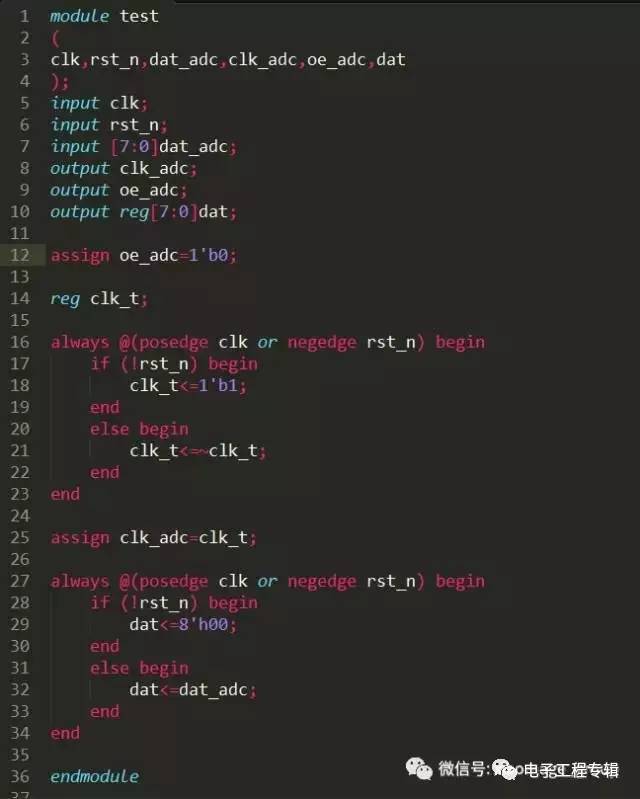

下面我们根据这两幅图进行FPGA的编程,在FPGA电路板中,系统时钟为50M,我们将其2分频为25M作为ADC的采样时钟。这个时候根据上面提到的采样率至少为输入信号频率的10倍原则,所以输入信号的最大频率为2.5MHz的正弦波。

对代码进行全局综合编译之后,开始分配引脚,引脚分配结束之后,我们今天使用Quartus ii的另一种工具:SignalTap II Logic Analysis,即Altera公司的一款内置逻辑分析仪,通过该功能,我们可以得到FPGA硬件运行的实际效果。但是它也有一个弊端,需要消耗FPGA的逻辑单元。

点开之后,会出现下图所示的界面,该界面中红色框标注的是比较重要的部分。

1,硬件仿真器

2,需要添加的触发信号,一般以系统时钟为触发信号

3,需要观察的信号,将自己所需的信号添加即可

以上三步设置完毕之后,保存,然后退出该界面,再次进行全局编译,编译无误之后,将程序下载入FPGA中,下载完成之后,再次打开该界面,然后点击手动运行图标,便可观察到FPGA实际运行的时序效果图。

第一张图的输入信号频率为2.5MHz,第二张图的输入信号频率为1MHz,第三章图的输入信号频率为100kHz。从以上三张图中可以看出,输入信号的频率越小,一个输入信号周期内采集的数据越多,波形越完整,也就是越逼近与实际波形。

- 上一篇:什么是三极管的倒置状态及它的作用 2017/5/18

- 下一篇:IGBT 鼻祖巴利迦教授首次来华讲演,万勿错过! 2017/5/18