长模组上的采样回路阻抗

2019-8-29 10:31:21 点击:

在特斯拉模组的设计上,我们看到了之前集中式BMS经常遇到的问题,这个采样线的长度和结合方式对于采样精度的影响。这个模组很长,FPC总体为了考虑成本,线也比较细,这个阻抗差异还是客观存在的。

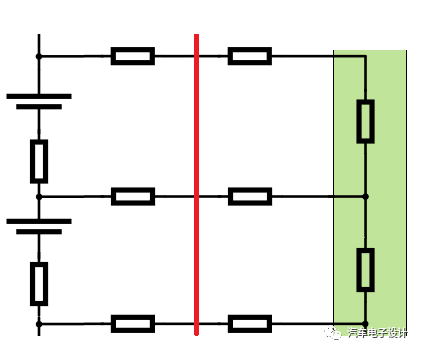

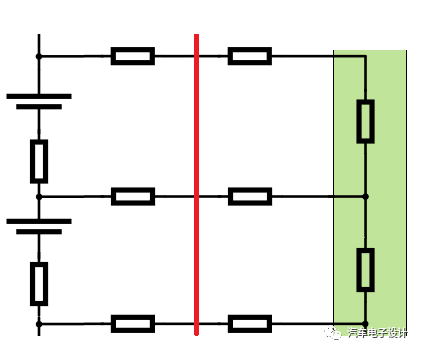

从等效电路的来看,在不同的工作状态下,采样环路内各个环节都可能造成采样精度偏差,在长模组里面,两个比较重要的差异点就是回路阻抗和AFE的漏电流。

在电池模组的回路阻抗里面,主要分为模组部分、BMU电路部分所组成

R模组部分:主要包括电芯的内阻+母排电阻(现在大容量的以DCR来看)、采样回路保险丝、Bonding线+FPC阻抗之和(单根是毫欧)

R BMS部分:采样通道串联电阻和AFE 芯片内部的等效电阻,这个滤波电阻往往考虑从百欧到千欧,主要和滤波电容匹配使用。

由于这个压降是和电阻和电流有关系的,考虑mV的压差,在不同的电流表征下的差异,我们可以根据以下的计算来看:

如果电源共线,在10-15mA级别,在50-100毫欧的模组内阻抗下造成0.5-1.5mV的差异,正常这个我们都是分离的

采样漏电流和采样电阻只有在板内造成差异,实际上在1kOhm的条件下*1uA下造成1mV的压降,由于均一性很强,其实还好

其实在较大电流均衡条件下,本身计算就是把校准做下去的,如果出现同电流压差变化大了,也可以做一些回路阻抗的判别

读取初始电压,这个电压等于V1'=V1-Inom*Rpathway

闭合均衡电路,读取V1''=V1-Ibalance*Rpahtway

通过记录这个数值来评估阻抗的合理性,实际上定值是Rbalance,根据电压来换算更为合理,V1''=V1-V''/Rbalance*Rpahtway

在这里的失效模式有几种:

采样回路开路、采样回路连接不良造成阻抗偏大、采样回路熔丝失效造成意外的电阻增大等,这个基本是靠诊断的方法来做的,通过对比采样数据的变化,防止整个ASIC芯片在处理过程中出现异常,我们也成为卡住为原有值。这种诊断意义,防止BMS某个电芯的电压读取异常。其步骤分为

读取每个电芯的电压

在纵向比较电芯的电压数据变化

在多数电芯由于电流波动产生变化时候,诊断电压采集卡住的那一路

在昨天双层模组设计的时候,这个线的差异倒是还好

小结:我们设计整合模式,一个是在长度扩展一个叠层扩展,采样线集中处理把CMU和模组分离还是一个趋势,我们希望尽可能把电池模组和电子部件分开,这样好处理一些,紧凑的长采样线设计还是需要我们尽快导入的

从等效电路的来看,在不同的工作状态下,采样环路内各个环节都可能造成采样精度偏差,在长模组里面,两个比较重要的差异点就是回路阻抗和AFE的漏电流。

在电池模组的回路阻抗里面,主要分为模组部分、BMU电路部分所组成

R模组部分:主要包括电芯的内阻+母排电阻(现在大容量的以DCR来看)、采样回路保险丝、Bonding线+FPC阻抗之和(单根是毫欧)

R BMS部分:采样通道串联电阻和AFE 芯片内部的等效电阻,这个滤波电阻往往考虑从百欧到千欧,主要和滤波电容匹配使用。

由于这个压降是和电阻和电流有关系的,考虑mV的压差,在不同的电流表征下的差异,我们可以根据以下的计算来看:

如果电源共线,在10-15mA级别,在50-100毫欧的模组内阻抗下造成0.5-1.5mV的差异,正常这个我们都是分离的

采样漏电流和采样电阻只有在板内造成差异,实际上在1kOhm的条件下*1uA下造成1mV的压降,由于均一性很强,其实还好

其实在较大电流均衡条件下,本身计算就是把校准做下去的,如果出现同电流压差变化大了,也可以做一些回路阻抗的判别

读取初始电压,这个电压等于V1'=V1-Inom*Rpathway

闭合均衡电路,读取V1''=V1-Ibalance*Rpahtway

通过记录这个数值来评估阻抗的合理性,实际上定值是Rbalance,根据电压来换算更为合理,V1''=V1-V''/Rbalance*Rpahtway

在这里的失效模式有几种:

采样回路开路、采样回路连接不良造成阻抗偏大、采样回路熔丝失效造成意外的电阻增大等,这个基本是靠诊断的方法来做的,通过对比采样数据的变化,防止整个ASIC芯片在处理过程中出现异常,我们也成为卡住为原有值。这种诊断意义,防止BMS某个电芯的电压读取异常。其步骤分为

读取每个电芯的电压

在纵向比较电芯的电压数据变化

在多数电芯由于电流波动产生变化时候,诊断电压采集卡住的那一路

在昨天双层模组设计的时候,这个线的差异倒是还好

小结:我们设计整合模式,一个是在长度扩展一个叠层扩展,采样线集中处理把CMU和模组分离还是一个趋势,我们希望尽可能把电池模组和电子部件分开,这样好处理一些,紧凑的长采样线设计还是需要我们尽快导入的

- 上一篇:如何实时有效地监测全方向蓄电池充电器无线充电的负载位置 2019/9/9

- 下一篇:UPS蓄电池发生漏液的危害 2019/8/29